Testing Neutron-Induced Soft Errors in Semiconductor Memories

| Participants: | N. Vijaykrishnan, Professor of Computer Science and Engineering |

| M. J. Irwin, Professor of Computer Science and Engineering | |

| Kenan Ünlü, Professor of Mechanical and Nuclear Engineering | |

| V. Degalahal, Ph.D. Student of Computer Science and Engineering | |

| S. M. Çetiner, Ph.D. Student of Mechanical and Nuclear Engineering | |

| Services Provided: | Neutron Beam Laboratory |

| Sponsor: | U.S. Department of Energy-Innovations in Nuclear Infrastructure and Eduaction (INIE) |

| Big-Ten Consortium Mini Grant Program |

Introduction

Soft errors are transient circuit errors caused due to excess charge carriers induced primarily by external radiations. Radiation directly or indirectly induces localized ionization that can flip the internal values of the memory cells. Our current work tries to characterize the soft error susceptibility for different memory chips working at different technology node and operating voltage.

Background and Related Work

Advances in VLSI technology have ensured the availability of high performance electronics for a variety of applications. The applications include consumer electronics like cellular phones and HDTVs; automotive electronics like those used in drive-by-wire vehicles, and million dollar servers used for storing and processing sensitive and critical data. These varied applications require not only higher throughput but also dependability. Even if a microprocessor is shipped without any design errors or manufacturing defects, unstable environmental conditions can generate temporary hardware failures. These failures, called transient faults, cause the processor to malfunction during operation time. The major sources of transient faults are electromagnetic interference, power jitter, alpha particles, and cosmic rays. Studies in [1, 2] have shown that a vast majority of detected errors originate from transient faults. Even a single-bit error may eventually lead to a computation failure. Therefore, managing the soft errors is a critical problem to solve in fully realizing dependable computing.

Soft error rate (SER) testing of devices has been performed for both neutron and alpha particles. Beam 30L of Weapon Neutron Research at the Los Alamos National Laboratory is a JEDEC prescribed test beam for soft errors, and is the only one of its kind. This beam is highly stable and it closely replicates the energy spectrum of terrestrial neutrons in the 2-800 MeV range while providing a very high neutron flux. The SER testing reported in literature recently were performed at this facility [4, 5]. However, the beam availability is limited. Alternatively in the past, experiments were carried out with alpha particles originating from 238Th foil on 0.25 µm-generation SRAMs [7]. Elimination of borophosphosilicate glass (BPSG) and 10B from the process flow in the 180-nm generation has made the low-energy (<1 eV) neutron SER negligible [3]. High-energy (1-1000 MeV) neutrons often dominate SER in advanced CMOS logic and memories. Hence, the need for accessible neutron testing facilities is critical for design of the next generation semiconductor devices.

This study intends to observe the effect of 10B and high energy neutrons on soft error rate. In order to investigate the effect of boron-10 on SER, a thermal neutron beam is used. For high-energy neutron testing, we intend to use the fast neutrons available near the reactor core by inserting a test circuit into a stand-up pipe adjacent to the reactor core face. This setup is shown in Figure 3.

Experimental Setup and results

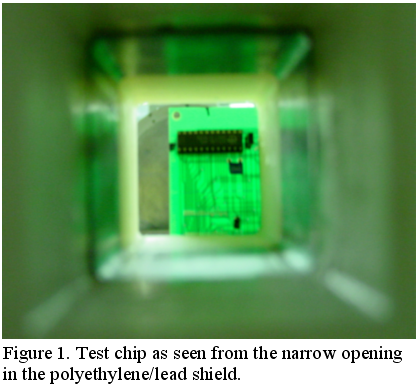

Penn State Breazeale Nuclear Reactor was used as the neutron source in the experiments. The maximum rated power of the reactor is 1 MW in the continuous mode, and 2000 MW in the pulse mode. The reactor power is adjusted from 10 W to 1MW observe the soft error rate dependence on neutron flux. No pulse-mode operation has been performed. Figures 1 and 2 show the test chip and the experimental setup.

For the beam port that was used in the experiments, the beam tube looks at the D2O tank to get a well-thermalized beam. The average thermal flux at the exit of the beam port is about 3´107 neutrons/cm2sec. The high neutron flux allows for accelerated testing of the phenomenon.

The experimental setup consists of a custom board interfaced with a computer through a GPIB card (from National Instruments). The board itself has off-the-shelf SRAM memory chips. The board is controlled through a LabVIEW interface. The controlling application consists of simple routines to read and write a user specified value across the whole memory. During the readout, it compares the written value to the value in each address.

The circuit board is secured in the beam cave, and connected to a PC outside using a 25-ft cable. This configuration allowed for continuous read-write, and for changing the operating conditions without interrupting the experiment.

The selected section of the board is tested on-line multiple times in the actual setup before the reactor is started. The board is exposed to neutron flux after the reactor reaches the stable power level.

As mentioned earlier, the neutron flux around the reactor core is much higher than that at the neutron beam ports. Therefore, the circuit board will also be placed by the periphery of the reactor core via a vertical standpipe in order to observe the effect of fast neutrons on soft error rate. A schematic drawing of fast neutron irradiation facility at PSBR is shown in Figure 3. The fast neutron flux at the core boundary is 5´1012 neutrons/cm2sec, and thermal flux is 1.3´1013 neutrons/cm2sec at 1MW steady state reactor operation. The reactor can be pulsed for a very short duration of time, around 10 milli-sec at its Full-Width Half-Maximum, at which it generates a fast flux of about 1´1016 neutrons/cm2sec at the core periphery. This amounts to about a ten order of magnitude increase in the fast flux. The time duration is very limited, yet the amount of fast flux is immense. The test circuits will be let inside the standpipe and the reading will be taken. In addition, the walls of the pipe will be covered with cadmium. Cadmium will absorb the thermal component of the flux so that the board is affected only by fast neutrons

Results and Discussion

The setup described in this report allows for accelerated testing of semiconductor memory devices with thermal and fast neutrons. The experiments and analyses have been performed only on soft errors due to thermal neutrons. Currently, a 16-kbit for Vendor A and a 4-Mbit memory from Vendor B were tested at various supply voltages and reactor power levels. The chip from Vendor A is rated to operate at 5V, but was found to operate as low as 3V. Figures 4 (a) shows the effect of changing the supply voltage on registered soft errors in one hour. A more salient behavior can be observed with the chip from Vendor B. Vendor B chip was known to be denser (4-Mbits compared to 16-kbits) and was expected to have higher soft error vulnerability. Figure 4 (b) shows the effect of supply voltage change on measured soft errors in one hour.

As presented in Equation 1 below, the soft error rate is expected to depend on the Qcritical and hence on the operating voltage.

SER = Nflux * CS * exp (−Qcritical/Qs) (1)

where Nflux is the intensity of neutron flux, CS is the area of cross section of the node, Qs is the charge collection efficiency, Qcritical is the charge that is stored at the node and hence is equal to VDD * Cnode, where VDD is the supply voltage and Cnode is the nodal capacitance. Figures 4 (a) and (b) confirm the exponential dependence of soft error rate on device operating voltage as well as other specifications of the device as pointed out by several authors before [7].

|

|

(a) |

(b) |

Figure 4. Effect of supply voltage on soft errors

While employing voltage scaling for power reduction, there is a reduction in the Qcritical of the cell. Now, if all the other factors remained the same there should be a super-linear increase in the SER. However, based on the Figures 4, we see a linear increase in the SER for a corresponding decrease in the voltage. This is because for a change in supply voltage, the resultant current transient also changes. As the supply voltage reduces, the magnitude of the current changes. This affects the regenerative feedback of the SRAM cell. Thus, the soft error rate is inversely proportional to the supply voltage.

For examining the statistical accuracy of the accelerated tests, the tests were performed at various reactor power levels. Since the reactor power and the flux at the exit of the beam port are directly correlated, changing the reactor power effectively changes the neutron flux impinging on the test sample, hence is expected to increase the soft error rate. The results are presented in Figures 5 (a) and (b).

|

|

(a) |

(b) |

Figure 5. Effect of neutron flux on soft errors

Both figures prove that the soft error rate increases as the reactor power increases. That the soft error rate for the chip from Vendor A is not as linear as the chip from Vendor B is attributed to the relatively small size of the first one. Hence, for statistical accuracy of accelerated soft error rate measurements, it is suggested that the measurements be performed using high capacity chips.

Future Work

This report briefly summarizes the first phase of the study that focused only on the effect of 10B fission caused by thermal neutron absorption on soft error rate. The elimination of BPSG layer in new device technologies and considerable reduction of 10B content in the p-dopant significantly dropped the contribution of boron fission as a source of soft error. Therefore, for younger-generation technologies, one needs to take into account the high-energy neutron impact on device operation for proper soft error rate analysis.

In the later phase, the circuit will be placed by the periphery of the reactor core in order to observe the effect of fast neutrons on soft error rate. The fast neutron flux at the core boundary is 5 ´ 10 12 neutrons/cm 2sec, and thermal flux 1.3 ´ 10 13 neutrons/cm 2sec at 1-MW steady state reactor operation.

The reactor can be pulsed for a very short duration of time, around 10 msec at FWHM, at which it generates a fast flux of about 1 ´ 10 16 neutrons/cm 2sec at the core periphery. This amounts to about a ten order of magnitude increase in the fast flux. The time duration is very limited, yet the amount of fast flux is immense. That might also reduce the experiment times significantly and help perform more tests with various technologies and designs.

References

[3] R. Baumann, The impact of technology scaling on soft error rate performance and limits to the efficacy of error correction, IEDM ’02 Technical Digest, IEEE International, pp. 329-332 , 8-11 Dec. 2002.

[4] P. Hazucha , T. Karnik, J. Maiz, S. Walstra, B. Bloechel, J. Tschanz, G. Dermer, S. Hareland, P. Armstrong, S. Borkar, Neutron soft error rate measurements in a 90-nm CMOS process and scaling trends in SRAM from 0.25-/spl mu/m to 90-nm generation, IEDM '03 Technical Digest, IEEE International, pp. 21.5.1-21.5.4, 8-10 Dec. 2003.

[5] J. Maiz , S. Hareland, K. Zhang, P. Armstrong, Characterization of multi-bit soft error events in advanced SRAMs,IEDM '03 Technical Digest, IEEE International, pp. 21.4.1-21.4.4, 8-10 Dec. 2003.

[6] N. Seifert, D. Moyer, N. Leland, R. Hokinson, Historical Trend in Alpha-Particle induced Soft Error Rates of the Alpha Microprocessor, IEEE 39th Annual International Reliability Physics Symposium, pp. 259-265, 2001.

[7] P. Hazucha and C. Svensson, Impact of CMOS Technology Scaling on the Atmospheric Neutron Soft Error Rate, IEEE Transactions on Nuclear Science, v. 47, No. 6, pp 2586-2594, Dec. 2000 .